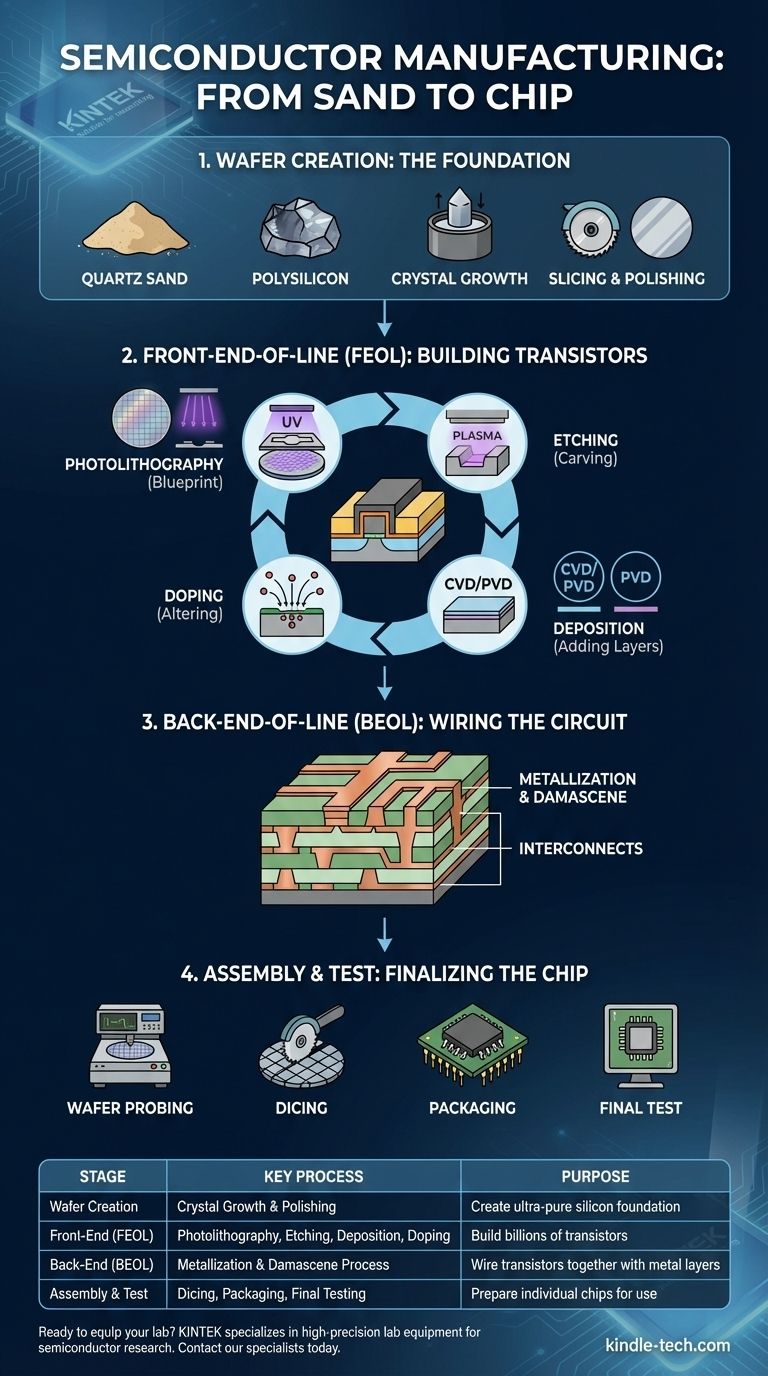

Im Grunde ist die Halbleiterfertigung ein Prozess, bei dem eine mikroskopisch kleine Stadt aus Milliarden elektronischer Schalter auf einem Wafer aus reinem Silizium aufgebaut wird. Dies ist keine einzelne Aktion, sondern eine hochkontrollierte Abfolge von Hunderten verschiedener Schritte, die grob in vier Hauptphasen unterteilt sind: Herstellung des Siliziumwafers, Fertigung der Schaltkreise auf dem Wafer (Front-End), Verdrahtung dieser Schaltkreise (Back-End) und schließlich Prüfung und Verpackung der fertigen Chips. Jede Phase erfordert ein Maß an Präzision, das zu den anspruchsvollsten in der gesamten modernen Industrie gehört.

Das zentrale Konzept, das man verstehen muss, ist, dass die Chipherstellung ein iterativer Zyklus von additiven und subtraktiven Prozessen ist. Materialschichten, manchmal nur Atome dick, werden akribisch auf einen Siliziumwafer abgeschieden, mithilfe von Licht strukturiert und dann selektiv weggeätzt, um nach und nach die Milliarden von Transistoren zu bilden, aus denen eine moderne integrierte Schaltung besteht.

Von Sand zu Silizium: Die Herstellung des Wafers

Bevor ein Schaltkreis hergestellt werden kann, muss das Fundament perfekt sein. Dieses Fundament ist eine nahezu fehlerfreie, ultrareine Scheibe aus Silizium, die als Wafer bezeichnet wird.

Das Rohmaterial: Polysilizium

Der Prozess beginnt mit Quarzkies (Siliziumdioxid), das erhitzt und gereinigt wird, um Silizium in metallurgischer Qualität herzustellen. Dieses wird dann weiter zu Polysilizium in Elektronikqualität verfeinert, einem Material, das zu 99,9999999 % rein ist. Diese extreme Reinheit ist nicht verhandelbar, da selbst die geringste Verunreinigung die elektrischen Eigenschaften eines Chips ruinieren kann.

Züchten des Ingots

Dieses Polysilizium wird in einem Tiegel geschmolzen. Ein winziger Impfkristall wird in das geschmolzene Silizium getaucht und unter Drehung langsam nach oben gezogen. Während es gezogen wird, kühlt das geschmolzene Silizium ab und erstarrt, wobei es der Kristallstruktur des Impfkristalls folgt. Dadurch entsteht ein großer Einkristallzylinder, der als Ingot oder „Boule“ bezeichnet wird und über zwei Meter lang sein und Hunderte von Kilogramm wiegen kann.

Schneiden und Polieren

Der zylindrische Ingot wird dann mit einer diamantbesetzten Säge in sehr dünne Scheiben geschnitten. Diese Rohscheiben, die als Wafer bezeichnet werden, werden geschliffen und zu einer spiegelglatten, fehlerfreien Oberfläche poliert. Ein typischer Wafer ist weniger als einen Millimeter dick, muss aber vollkommen eben sein.

Das Herzstück der Chipherstellung: Front-End-of-Line (FEOL)

Hier werden die Transistoren – die grundlegenden Ein-/Ausschalter eines Chips – direkt auf der Oberfläche des Siliziumwafers aufgebaut. Dies geschieht durch einen sich wiederholenden Zyklus von vier Hauptprozessen.

Schritt 1: Fotolithografie (Der Bauplan)

Die Fotolithografie ist der wichtigste Einzelschritt bei der Chipherstellung. Eine Schicht aus lichtempfindlichem Material, genannt Photoresist, wird auf den Wafer aufgetragen. Eine Maske, die wie eine Schablone mit dem Bauplan für eine Schicht des Schaltkreises fungiert, wird über dem Wafer positioniert. Dann wird eine bestimmte Wellenlänge von Licht (häufig tiefes Ultraviolett oder DUV/EUV) durch die Maske projiziert, wodurch die chemische Struktur des belichteten Photoresists verändert wird.

Schritt 2: Ätzen (Muster schnitzen)

Der Wafer wird dann Chemikalien oder Plasma ausgesetzt, die den weich gewordenen Photoresist entfernen. Dadurch bleibt eine gemusterte Schicht aus gehärtetem Photoresist zurück, die einige Bereiche des Wafers schützt, während andere freigelegt werden. Beim Ätzprozess wird ein Gas (Trockenätzen) oder eine Flüssigkeit (Nassätzen) verwendet, um das Material aus den freigelegten Bereichen zu entfernen und so das Schaltkreismuster in die darunter liegende Schicht zu schnitzen.

Schritt 3: Abscheidung (Hinzufügen neuer Schichten)

Nach dem Ätzen werden neue Materialschichten auf den Wafer aufgebracht. Die Chemical Vapor Deposition (CVD) ist ein Verfahren, bei dem Gase reagieren, um einen festen Film auf dem Wafer zu bilden, der zur Erzeugung isolierender (dielektrischer) Schichten verwendet wird. Die Physical Vapor Deposition (PVD) oder Sputtern bombardiert ein Zielmaterial mit Ionen, wodurch Atome herausgeschlagen werden, die sich dann auf dem Wafer abscheiden, was häufig für Metallschichten verwendet wird.

Schritt 4: Dotierung (Änderung der Leitfähigkeit)

Damit ein Transistor funktioniert, müssen die elektrischen Eigenschaften des Siliziums selbst verändert werden. Dies geschieht durch Ionenimplantation, einem Prozess, bei dem ein Teilchenbeschleuniger mit hoher Energie spezifische Ionen (wie Bor oder Phosphor) in den Siliziumwafer schießt. Diese „Dotierung“ erzeugt die negativ-leitenden (N-Typ) und positiv-leitenden (P-Typ) Bereiche, die es einem Transistor ermöglichen, ein- und ausgeschaltet zu werden.

Dieser Zyklus aus Lithografie, Ätzen, Abscheidung und Dotierung wird Hunderte Male wiederholt, um die komplexen, dreidimensionalen Strukturen moderner Transistoren aufzubauen.

Verbindung der Transistoren: Back-End-of-Line (BEOL)

Sobald die Milliarden von Transistoren in der FEOL-Stufe gebildet sind, müssen sie miteinander verdrahtet werden. Diese „Verdrahtung“, bekannt als Interconnect, ist ein dichtes, mehrschichtiges Gitter aus Kupfer- oder Aluminiumbahnen, das auf den Transistoren aufgebaut wird.

Der Metallisierungsprozess

Der BEOL-Prozess ähnelt stark dem FEOL, konzentriert sich jedoch auf die Erstellung leitfähiger Bahnen anstelle von Transistoren. Eine Schicht Isoliermaterial wird abgeschieden, und dann werden Lithografie und Ätzen verwendet, um Gräben und Vias (vertikale Verbindungen) zu erzeugen, wo die Drähte verlaufen sollen.

Aufbau der Verdrahtungsschichten

Diese Gräben werden dann in einem Prozess namens Damascene mit Kupfer gefüllt. Das überschüssige Kupfer auf der Oberfläche wird wegpoliert, sodass eine vollkommen ebene Schicht mit eingelassener Kupferverdrahtung entsteht. Dieser Prozess wird wiederholt, um ein komplexes „Autobahnsystem“ aus 10-20 Verdrahtungsschichten aufzubauen, das alle einzelnen Transistoren zu einem funktionierenden Schaltkreis verbindet.

Verständnis der Kompromisse und Herausforderungen

Der Halbleiterfertigungsprozess ist durch seine extremen Herausforderungen definiert. Erfolg wird daran gemessen, wie gut man diese meistern kann.

Die Tyrannei der Sauberkeit

Ein moderner Transistor ist so klein, dass ein einzelner Staubkorn wie ein riesiger Felsbrocken wirkt, der einen Schaltkreis kurzschließen und einen ganzen Chip zerstören kann. Deshalb werden Chips in Reinräumen hergestellt, Anlagen, die tausendmal sauberer sind als ein chirurgischer Operationssaal. Arbeiter müssen Ganzkörper-„Boonie-Suits“ tragen, um Kontamination zu verhindern.

Das Streben nach kleineren Nennwerten

Der Fortschritt der Branche wird durch die Verkleinerung der Transistoren vorangetrieben, ein Trend, der durch das Mooresche Gesetz beschrieben wird. Diese „Prozessknoten“ (z. B. 7 nm, 5 nm) beziehen sich auf die Größe der Merkmale auf dem Chip. Wenn die Merkmale schrumpfen, werden physikalische Herausforderungen wie der Quantentunnel-Effekt – bei dem Elektronen durch Isolatoren lecken – signifikant und erfordern neue Materialien und Transistordesigns (wie FinFETs).

Ausbeute (Yield): Die ultimative Erfolgsmetrik

Die Ausbeute (Yield) ist der Prozentsatz der funktionierenden Chips pro Wafer. Da der Prozess Hunderte von Schritten umfasst, kann ein winziger Fehler in einem beliebigen Stadium einen Defekt verursachen. Eine Ausbeute von 90 % mag hoch erscheinen, bedeutet aber, dass 10 % der unglaublich teuren Produktion wertlos sind. Eine Verbesserung der Ausbeute um nur 1-2 % kann zu zusätzlichen Einnahmen in Millionenhöhe führen.

Fertigstellung des Chips: Montage und Test

Nach Hunderten von Schritten enthält der Wafer Hunderte oder Tausende einzelner Chips, die als Dies (Einzelchips) bezeichnet werden.

Wafer-Test und Zerteilen (Dicing)

Zuerst testen automatisierte Sonden jeden einzelnen Die auf dem Wafer, um festzustellen, welche funktionsfähig sind. Anschließend wird der Wafer in einzelne Dies gesägt, ein Prozess, der als Dicing bezeichnet wird.

Verpackung und Endtest

Die funktionierenden Dies werden dann zur Verpackung geschickt. Der winzige, zerbrechliche Siliziumdie wird auf ein Substrat montiert und in ein schützendes Kunststoff- oder Keramikgehäuse eingekapselt. Dieses Gehäuse stellt die Metallstifte oder -flächen bereit, die den Chip mit der Außenwelt verbinden. Nach der Verpackung durchläuft der Chip einen letzten, strengen Test, bevor er versandt wird.

Warum dieser Prozess wichtig ist

Das Verständnis der Grundlagen der Chipherstellung liefert einen entscheidenden Kontext für die gesamte Technologielandschaft.

- Wenn Ihr Hauptaugenmerk auf Ingenieurwesen oder Forschung liegt: Erkennen Sie, dass der iterative Zyklus aus Lithografie, Ätzen, Abscheidung und Dotierung der grundlegende Baustein aller modernen Elektronik ist.

- Wenn Ihr Hauptaugenmerk auf Wirtschaft oder Investitionen liegt: Verstehen Sie, dass die Ausbeute, die immensen Kapitalkosten einer Fertigungsanlage (Fab) und das unerbittliche Rennen um kleinere Prozessknoten die Haupttreiber für den Marktettbewerb und die Dynamik der Lieferkette sind.

- Wenn Ihr Hauptaugenmerk auf Technologie im Allgemeinen liegt: Würdigen Sie, dass das Smartphone in Ihrer Hand oder der Server in der Cloud das Ergebnis eines der komplexesten, präzisesten und teuersten Herstellungsprozesse ist, die die Menschheit je entwickelt hat.

Letztendlich wird die digitale Welt nicht nur durch clevere Software aufgebaut, sondern auf einem physischen Fundament aus angewandter Physik und Fertigungspräzision in einem fast unvorstellbaren Maßstab.

Zusammenfassungstabelle:

| Stufe | Schlüsselprozess | Zweck |

|---|---|---|

| Wafer-Erstellung | Kristallwachstum & Polieren | Schaffen eines ultrareinen Siliziumfundaments |

| Front-End (FEOL) | Fotolithografie, Ätzen, Abscheidung, Dotierung | Aufbau von Milliarden von Transistoren |

| Back-End (BEOL) | Metallisierung & Damascene-Prozess | Verdrahtung der Transistoren mit Metallschichten |

| Montage & Test | Dicing, Verpackung, Endtest | Vorbereitung einzelner Chips zur Verwendung |

Bereit, Ihr Labor für Halbleiterforschung oder -produktion auszustatten? KINTEK ist spezialisiert auf hochpräzise Laborgeräte und Verbrauchsmaterialien, die für Halbleiterfertigungsprozesse unerlässlich sind, einschließlich Abscheidungssystemen, Ätzwerkzeugen und Wafer-Handling-Lösungen. Unsere Expertise gewährleistet die Zuverlässigkeit und Reinheit, die Ihre Arbeit erfordert. Kontaktieren Sie noch heute unsere Spezialisten, um zu besprechen, wie wir die spezifischen Anforderungen Ihres Labors in der Halbleiterindustrie unterstützen können.

Visuelle Anleitung

Ähnliche Produkte

- Optisches Fensterglas Substratwafer Quarzplatte JGS1 JGS2 JGS3

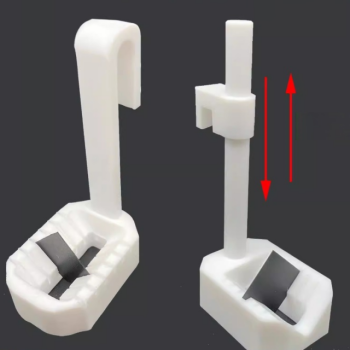

- Anpassbare PTFE-Waferträger für Halbleiter- und Laboranwendungen

- Vielseitige PTFE-Lösungen für die Halbleiter- und medizinische Waferverarbeitung

- Siliziumkarbid (SiC) Keramikplatte Verschleißfeste technische fortschrittliche Fein Keramik

- Kundenspezifische PTFE-Waferhalter für Labor und Halbleiterfertigung

Andere fragen auch

- Was ist die maximale Temperatur für Quarzfenster? Gewährleistung der langfristigen Zuverlässigkeit und Vermeidung von Entglasung

- Was ist die Arbeitstemperatur von Quarzglas? Meistern Sie seine Hochtemperaturgrenzen und Anwendungen

- Wie unterscheidet sich Quarz von Glas? Ein Leitfaden zur Materialauswahl für die Leistung

- Ist Quarz ein widerstandsfähiges Mineral? Entdecken Sie die zwei Formen von Quarz und ihre einzigartigen Stärken

- Welchen Temperaturbereich hat Quarzglas? Beherrschen Sie seine thermischen Grenzen für anspruchsvolle Anwendungen